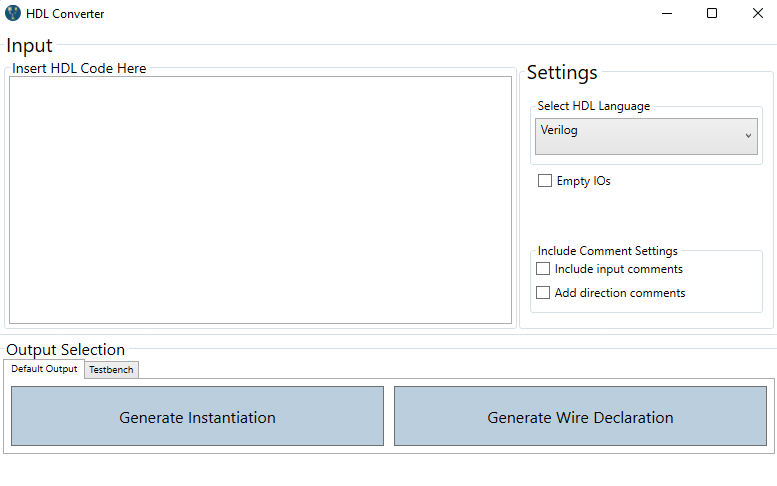

Description

A simple tool that can be used to convert the header syntax of a verilog module or VHDL Entity to an instantiation syntax and create testbench structures (top level and verify). The project is aimed at removing the need for tedious refactoring of module headers when instantiating modules or verifying individual modules with testbenches.

Features Included

- Conversion of Verilog or VHDL header/entity to instantiation of the module

- Conversion of Verilog or VHDL header/entity to declare all wires in the module

- Automatic generation of testbench structure (testbench toplevel, verify module)

- Comment creation for instantiaton making port direction easily visible

- Parsing of Verilog/VHDL header syntax to objects and attributes (easy expandability to othre hdl code generations functions)

- Flexibility to support other HDL languages